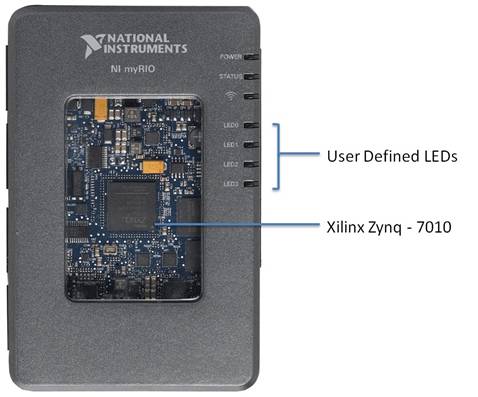

NI myRIO Hardware Overview

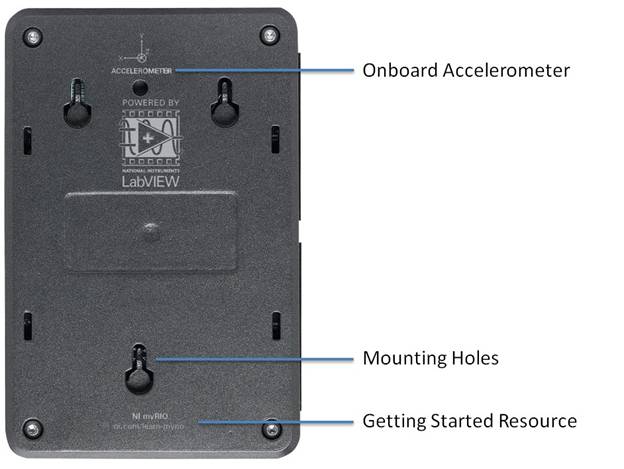

NI myRIO is a revolutionary hardware/software platform that gives students the ability to “do engineering” and design real systems more quickly than ever before. Complete with the latest Zynq integrated system-on-a-chip (SoC) technology from Xilinx, the NI myRIO boasts a dual-core ARM® Cortex™-A9 processor and an FPGA with 28,000 programmable logic cells, 10 analog inputs, 6 analog outputs, audio I/O channels, and up to 40 lines of digital input/output (DIO). Designed and priced for the academic user, NI myRIO also includes onboard WiFi, a three-axis accelerometer, and several programmable LEDs in a durable, enclosed form factor.

Front View

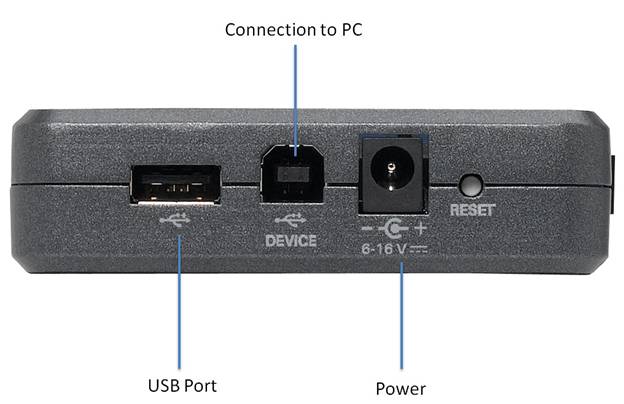

Back View

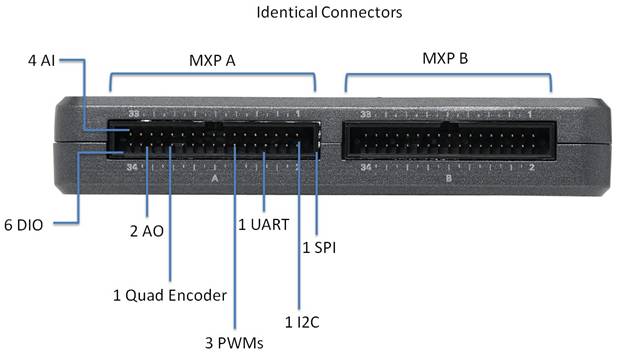

myRIO Expansion Port (MXP) Connectors

The default I/O configuration is shown. It is customizable with the NI LabVIEW FPGA Module. These are 0.1″ pitch dual-row 34-position (17 x 2) IDC connectors.

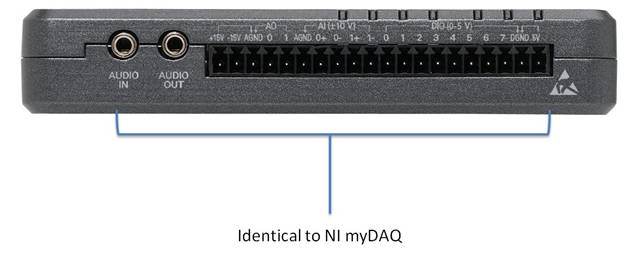

myRIO miniSystems Port (MSP) Connector

The default I/O configuration is shown. It is customizable with LabVIEW FPGA.

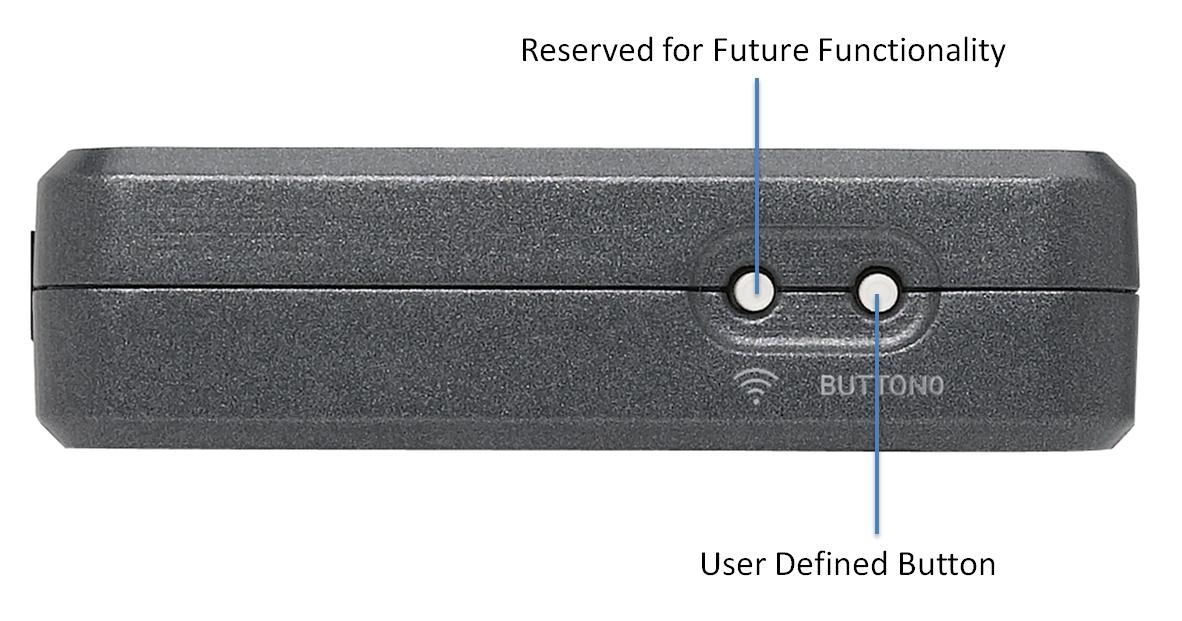

Top View View

Bottom View

myRIO Developer’s Essentials Guide for Academia

by Ed Doering

This is a very thorough guide to using the myRIO that includes the following sections:

- Introduction and Software Setup

- RIO

- Academic RIO

- Application Examples

- Make your first RT Application

- Make your first FPGA Application